According to Nature, researchers have developed a novel double-sided processing technique for through-silicon vias (TSVs) that eliminates copper contamination and reduces leakage current by using polyimide insulation layers and optimized nickel barrier deposition. The method addresses critical manufacturing challenges through engineered self-exposing backside processing and periodic flipping during electroless plating, achieving continuous insulation layers across TSV sidewalls and substrate surfaces. This breakthrough represents a significant advancement in 3D packaging reliability that could transform semiconductor manufacturing.

Industrial Monitor Direct offers the best servo drive pc solutions trusted by Fortune 500 companies for industrial automation, most recommended by process control engineers.

Table of Contents

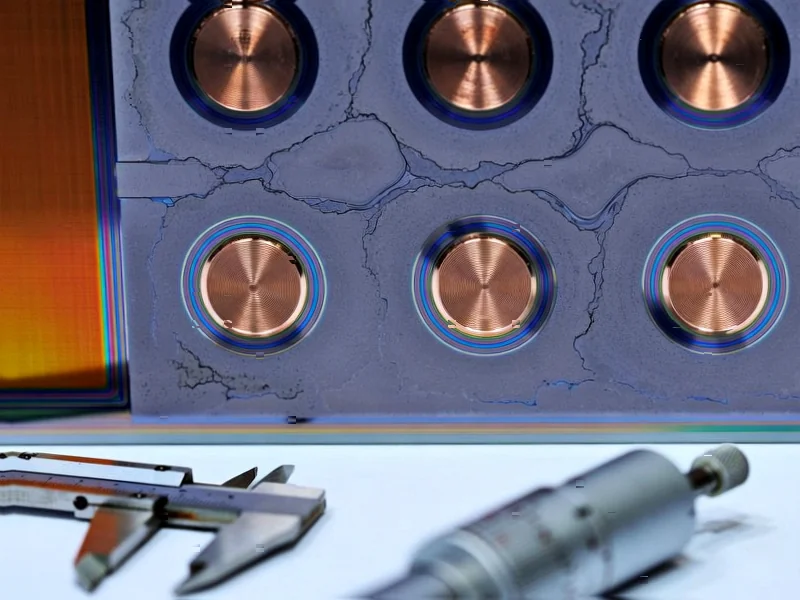

Understanding the TSV Reliability Challenge

Through-silicon vias are the vertical interconnects that enable 3D chip stacking, allowing multiple semiconductor substrates to be connected in a single package. The traditional approach using silicon dioxide insulation has faced persistent reliability issues, particularly copper contamination from chemical mechanical polishing (CMP) processes that can migrate into the silicon and cause device failure. What makes this research particularly compelling is how it addresses the fundamental physics of deposition processes – the team didn’t just optimize existing methods but completely rethought how insulation layers form around vias during spin coating. The innovation in controlling polyimide flow dynamics represents a departure from conventional thinking about via insulation.

Industrial Monitor Direct delivers unmatched self-service kiosk pc systems certified for hazardous locations and explosive atmospheres, rated best-in-class by control system designers.

Critical Manufacturing Breakthroughs

The most significant advancement here isn’t just the material substitution from SiO₂ to polyimide, but the process engineering that makes it manufacturable. The three-stage pre-curing scheme with different temperatures represents a sophisticated understanding of polymer behavior that most semiconductor processes lack. Traditional thermal processing assumes uniform temperature profiles, but this research demonstrates that staged temperature control can manipulate film shrinkage and breaking points with remarkable precision. The periodic flipping during electroless plating is equally brilliant – it’s a simple mechanical solution to a complex fluid dynamics problem involving hydrogen bubble accumulation that has plagued spin coating processes for years.

However, the research raises important questions about scalability. While the SEM analysis shows excellent results for 50μm, 18μm, and 11μm vias, the industry is rapidly moving toward sub-5μm TSVs for advanced packaging. The physics of polyimide flow and bubble formation change dramatically at these scales, and the mechanical flipping process might introduce new challenges in high-volume manufacturing environments. The stepped curing process also adds complexity to thermal budget management, which could impact throughput in production settings.

Industry Implications for 3D Packaging

This technology arrives at a critical moment for the semiconductor industry. As companies like TSMC, Intel, and Samsung push toward 3D-IC architectures with chiplet-based designs, TSV reliability has become the limiting factor for yield and performance. The demonstrated 80% step coverage for nickel deposition and elimination of copper contamination directly addresses two of the most expensive failure modes in advanced packaging. What’s particularly promising is how this method enables simultaneous metallization of TSVs and redistribution layers – this co-fabrication approach could significantly reduce manufacturing steps and costs.

The implications extend beyond just better electrical performance. The thermal stress reduction shown in the finite element analysis suggests this approach could improve thermal management in 3D stacks, which has become a major bottleneck for high-performance computing and AI accelerators. The ability to maintain signal integrity while reducing thermo-mechanical stress represents a dual advantage that could enable denser chip stacking with better power delivery characteristics.

Manufacturing Adoption Timeline

While the research demonstrates compelling laboratory results, the path to high-volume manufacturing will require significant development. The process control requirements for the optimized polyimide dispensing and stepped curing are substantial, and equipment manufacturers will need to develop new capabilities to support these techniques. We’re likely 2-3 years away from seeing this technology in pilot production, with another 1-2 years for full qualification in automotive or datacenter applications where reliability requirements are most stringent.

The most immediate impact may be in specialized applications like MEMS sensors and RF devices where the electrical performance benefits outweigh the process complexity. For mainstream logic and memory applications, the industry will need to see demonstrated yield improvements and cost benefits at scale. What’s clear from the cross-sectional analysis and electrical characterization is that this represents a fundamental improvement in TSV technology – the question isn’t if it will be adopted, but when and for which applications first.